AMDではCPUダイの上に巨大なキャッシュ用メモリーを重ねて搭載する3D V-Cache技術を2021年6月に発表し、2022年4月20日にはそれらを市販化したRyzen 7 5800X3Dが発売されますが、AMDではこの技術を更に応用してRyzenやEPYCなどAMD製CPUに搭載されているI/Oダイ上に機械学習用のアクセラレータなど様々な機能を持つ半導体を重ねて搭載する事を検討しているようです。

3D V-Cacheなど3Dスタッキング技術と追加アクセラレータ

AMDではCOMPUTEX2021にて「3D Chiplets」となるパッケージング技術を発表、その最初の製品としてCPUダイの上に巨大なメモリー用ダイを重ねて搭載する3D V-Cacheを発表し、2022年4月20日にはRyzen 7 5800X3Dなど3D V-Cacheを搭載したCPUが発売されます。

AMDではこの3D Chipletsパッケージング技術を応用する方針のようで、2022年末に投入が予定されているRDNA3アーキテクチャーを搭載するRadeon RX 7000シリーズでは複数のGPUダイが搭載されるMCMとなりますが、その中でGPU間の通信を担うI/Oダイの上にInfinity Cacheが搭載されるなど3D Chipletsパッケージング技術が応用される見込みになっています。

そんな、AMDの3D Chipletsパッケージング技術ですが、将来的にこれらを更に応用してRyzenやEPYCなどチップレットデザインを採用するCPUに搭載されているI/Oダイ上に機械学習用のアクセラレータなど様々な機能を重ねて搭載する事を検討しているようです。また、I/Oダイが様々な機能を繋ぐハブとしての役割を担う構想もあるようです。

AIや機械学用アクセラレータをI/Oダイの上に搭載

AMDが2020年9月25日に申請した特許情報によると、AMDではI/Oダイに様々な機能を追加する事を考えているようです。その一つがI/Oダイ上にAIおよび機械学習用のアクセラレーターを搭載するという物で、特許名はDirect connected machine learning accelerator、日本語訳すると直接接続された機械学習用アクセラレータとなります。

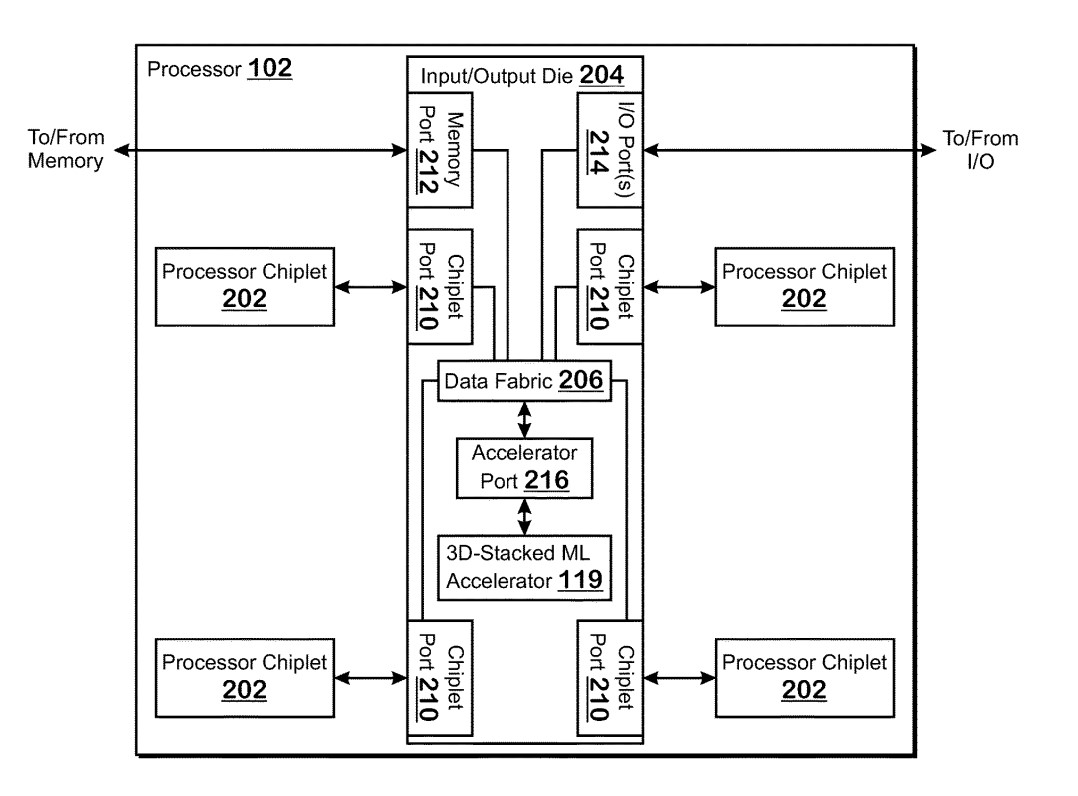

特許情報ではI/OダイとしてメモリーやI/Oポート、プロセッサへ繋がるチップレットなど現行のRyzenやEPYCに搭載されているI/Oダイと変わらない役割が示されていますが、これに追加で『アクセラレータポート』そして『3D-Stacked MLアクセラレータ』と言う新しい機能に関して記載が出現しています。

3D-Stacked MLアクセラレータと言う事で、AMDでは機械学習用を行うFPGAやGPUなどをI/Oダイ上に新たに設けるアクセラレータポートを通じて積層して搭載する事を考えているようです。

機械学習用アクセラレータなどはApple M1などに搭載されており、コンシューマー向けでも徐々に使われ始めていますが、Apple M1のようにCPUダイに機械学習用アクセラレータを搭載するとなると、ダイサイズの肥大化や設計や製造にかかる時間やコストが増大する事となります。

そのため、AMDとしてはI/Oダイ上にアクセラレータポートと呼ばれる接続用のスペースを用意しておき、必要に応じて機械学習用アクセラレータを上に搭載するという手法を取る事で機械学習用アクセラレータをより低い開発コストと製造コストで搭載しようと考えているようです。

なおこの特許が出願された2020年9月25日と言うのはFPGAなどを開発するXilinxがAMDに買収されると公表される1ヵ月ほど前になっており、もしかしたらXilinxとAMDがタッグを組んだ製品が2023年に登場すると言われている事からこの特許に関連した製品が登場するかもしれません。

『アクセラレーターポート』を使ってCPUに様々な機能をトッピング?

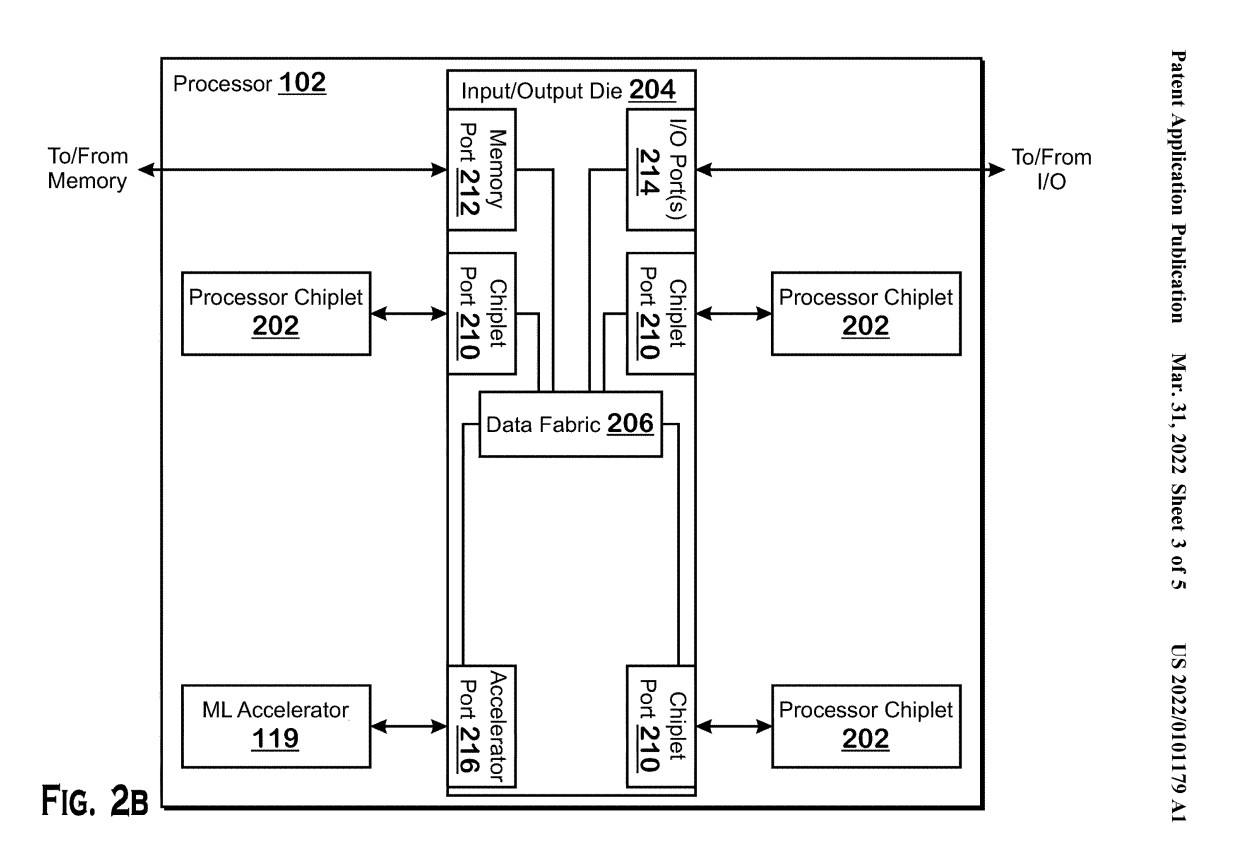

特許情報ではI/Oダイに直接機械学習用アクセラレータを搭載する事が記載されており、これには『アクセラレータポート』が重要な役割を担っていましたがAMDではこの『アクセラレータポート』を活用してCPUに様々な機能を追加する事を考えているようです。

これが、Fig.2Bで記載されている図で、機械学習用アクセラレータが別のダイとして搭載され、それがアクセラレータポートに接続されるというものでAMDではこの機械学習用アクセラレータの他にGPUやDSP、ASIC、FPGAなど様々な機能を追加を想定しているとの事です。

用途別のダイをCPUに搭載するという手法はI/Oダイ上に機械学習用アクセラレータを重ねるという戦略と同じく、CPUダイの肥大化を防ぐ事が可能になっていますが、I/Oダイ上に重ねるほど小型化が難しいモノ、例えばGPUなどではこのように一つのダイとして搭載する方が汎用性が高く、もし本当に出現するのであれば用途に応じてI/Oダイの上に搭載するか、別ダイとして搭載するかなど細かく仕様が分かれるモノと見られています。

今回の情報は特許情報であるため、必ず実現するモノではないと認識する必要はありますが、考え方としては合理的と思います。と言うのもCPUダイなどに組み込んで機械学習用アクセラレータを搭載するとなるとダイサイズも大きくなり、CPUまたは機械学習用のどちらかに設計変更が生じた際には双方に再確認や再設計の被害が出ます。一方で、CPUと機械学習を別のダイとして搭載となれば、開発時はCPUと機械学習でそれぞれ独自のロードマップで開発が行え、最新技術をそれぞれの製品に詰め込むことが出来ると見られます。

今後、データセンター向けはもちろんの事、コンシューマー向けCPUでもApple M1のように機械学習などハードウェアアクセラレータが搭載されるなど重要性は増しており、近い将来何かしらこの特許で記載された事が採用された製品が出る可能性は高そうと言えそうです。

コメント